PCIe Gen 6的演进与洞察

PCle协议 (外围组件互连Express)于2003年推出第一代,在串行计算机扩展总线中每通道允许高达2.5 GT/s的速度,成为业界的一项巨大突破。

此后,该协议已经发展了多次,与上一代相比,其传输速率始终翻倍,并在需要时引入新功能和优化。最新版本于2022年发布,其中引入了PCle 6.0,每通道速度高达64.0 GT/s。正如2023年在圣何塞举行的PCI-SIG开发者大会上宣布的那样,PCle 6.0不仅再次将速度提高了一倍,而且为未来的许多代产品奠定了基础。此次修改是考虑到对现有规则的许多必要优化,考虑到20年的行业使用和经验。引入了新的概念和技术,例如1b/1b编码、PAM4调制和Flit模式操作。

PCle 6.0规范中所有功能的更改都是考虑到需要进行优化以跟上更高的吞吐率。因此,遵循以下准则:

- 减少损失:通过避免不必要的编码;

- 做出假设:基于既定模式;

- 避免传输不必要的信息:可能被对方推断出来;

- 避免重新配置:如果之前已经配置过。

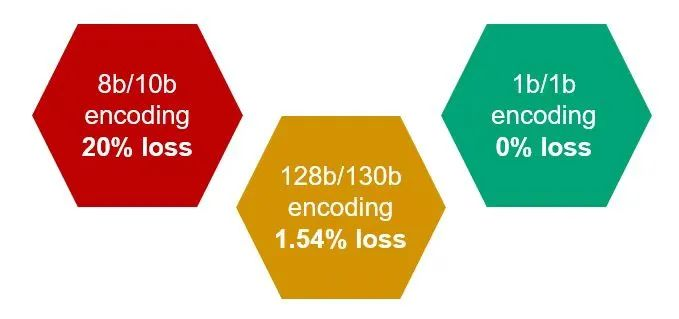

PCle 6.0中引入的新编码是通过避免不必要的编码来减少损失的最大例子。以前,实例在以8.0GT/s或更高速度运行时使用128b/130b编码。这意味着每128位数据需要2个额外位才能被另一方正确解码。这导致串行链路效率低下,仅由于编码就损失了1.54%的比特级带宽。

1b/1b通过保证传输的每一位都可以被另一方用作实际信息来解决这个问题。这是通过在预期数据类型的每一侧实施内部计数器来完成的。只要正确验证设计以遵守这些计数器,就可以保证它们能够进行通信,而无需在链接中发送任何额外的不必要的信息。

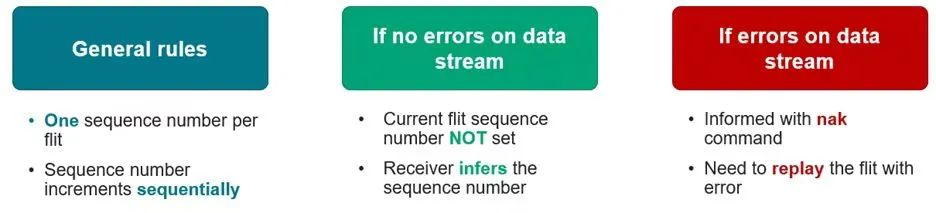

fit序列号是PCle6.0中引入的新概念,与fit操作模式一起添加。它取代了事务层数据包(TLP)中存在的旧序列号及其确认或重播机制。以前,序列号总是附加到每个传输的TLP上。尽管它增加了链接的稳健性,但考虑到TLP具有连续的序列号,这被证明是一种资源浪费。因此,知道一个TLP的序列号意味着知道它旁边的TLP的编号,依此类推。

fit 序列号协议通过实现隐式序列号对此进行了优化,其中序列号由另一方推断。不仅如此,序列号也处于fit级别,可以同时容纳很多TLP。因此,先前用于始终发送的序列号信息的空间可用于增加有用信息的带宽。

以前,在连接后更改链路宽度的过程对于设备来说成本高昂,因为他需要检查链路训练和状态机制 (LTSSM)的所有配置状态。这意味着重新配置通道的所有细节,尽管唯一需要更改的 变量是所使用的链路密度。

PCie 6.0中通过引入仅在Fiit 模式中存在的LO部分(LOp)功能进行了增强。执行LOp序列可以在活动数据传输期间更改链路密度,而无需关闭链路。这意味着通过更改链路密度来实现节能更加有效 ,而且设备可以轻松保持较小的宽度,以防出現热节流问题。

综上所述,PCle 6.0带来了很多变化,这些变化都是为了保证PCle协议的各个层都能跟上更高的传输速率而进行的优化。目前正在进行的PCle7.0在所有这些变化的基础上,继续了对PCle的支持和优化。因此,验证设备是否遵循所有这些功能的功能行为非常重要,以确保它们能够从新一代协议以及尚未发布的版本提供的优势中受益。